The MOS Technology 6502 CPU was a popular part in its day. In various modified versions, it powered everything from the Commodore 64 to the Nintendo Entertainment System, and showed up in a million other applications too. A popular variant is the 65C02, and [Jürgen] decided to whip up a pin-compatible FPGA version that runs at a blazing 100MHz.

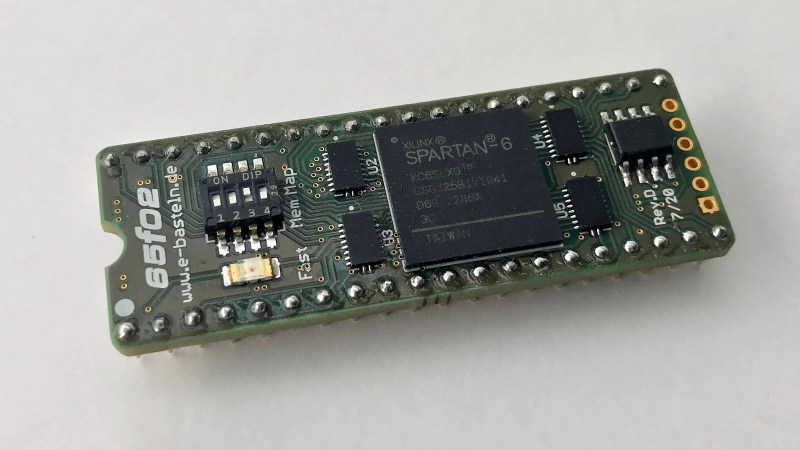

The CPU core was borrowed from work by [Arlet Ottens] and extended with 65C02 functionality by [Ed Spittles] and [David Banks]. [Jürgen] then packaged that core in a Spartan-6 FPGA and placed it on a small PCB the size of the original 65C02’s 40-pin dual inline package.

The FPGA is set up to access the external CPU bus with the timing matched to the clock of the host machine. However, internally, the CPU core runs at 100MHz. It copies RAM and ROM from the host machine into its own internal 64 kilobyte RAM, minus the areas used for memory-mapped I/O by the host. The CPU then runs at full 100MHz speed except when it needs to talk to those I/O addresses.

It allows the chip to accelerate plenty of tasks without completely flipping out when used with older hardware that can’t run at anywhere near 100MHz. The pin-compatible design has been tested successfully in an Apple II and a Commodore 8032, as well as a variety of vintage chess computers.

We’ve seen the opposite before too, with a real 6502 paired with a FPGA acting as the rest of the computer. If you’ve got any cutting-edge 6502 hacks of your own (not a misprint!), let us know!

[Thanks to David Palmer for the tip]

0 Commentaires