From the consumer space it often would appear as if Intel’s CPU making history is pretty much a straight line from the 4004 to the 8080, 8088 and straight into the era of Pentiums and Cores. Yet this could not be further from the truth, with Intel having churned through many alternate architectures. One of the more successful of these was the Intel i960, which is also the topic of a recent article by [Ken Shirriff].

Remarkably, the i960 as a solid RISC (Reduced Instruction Set Computer) architecture has its roots in Intel’s ill-fated extreme CISC architecture, the iAPX 432. As [Ken] describes in his comparison between the i960 and 432, both architectures are remarkably similar in terms of their instruction set, essentially taking what it could from the 432 project and putting it into a RISC-y shape. This meant that although the i960 could be mistaken as yet another RISC CPU, as was common in the 1980s, but integrated higher-level features as well, such as additional memory protection and inter-process communication.

Although there were four versions of the i960 sold, they all used the same die, just with some parts not connected. The high-end XA version can be regarded as a 33-bit processor due to the full architecture’s features being enabled, including the entire ISA and object model. A year after the initial i960 release, the CA version would become the world’s first superscalar processor, and as a whole the i960 processor became a popular sight in the US military, also due to the way it worked well with the US-mandated use of the Ada programming language. In a way this fulfilled many of the promises the iAPX 432 had made.

Despite the successes, ultimately the i960 was axed by Intel after it had been neglected for many years in favor of the x86 architecture, until in 2007 the production of i960 processors finally ceased.

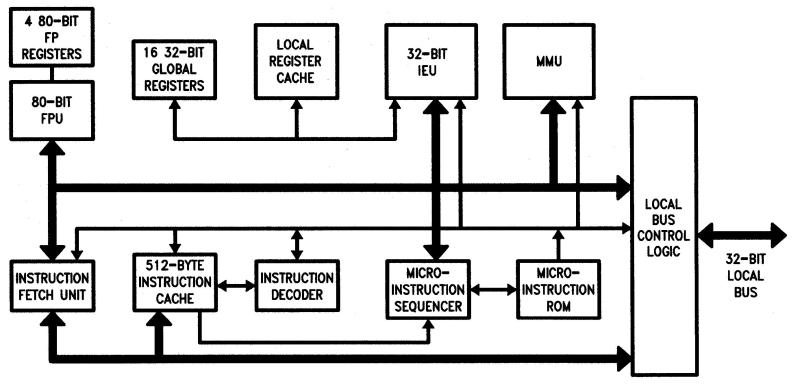

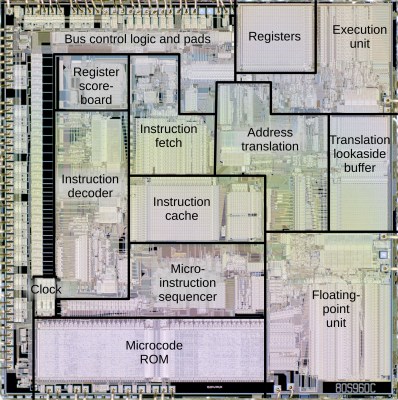

(Heading image: The microarchitecture of the i960 XA. FPU is Floating Point Unit. IEU is Instruction Execution Unit. MMU is Memory Management Unit. From the 80960 datasheet.)

0 Commentaires